# Mu3e pixel chip "MuPix" and module construction design overview for the meeting with UK institutes

Frank Meier Universität Heidelberg

March 31, 2016

### Overview

Introduction

MuPix7

Towards MuPix8

Flexprint

Conclusions

#### Introduction

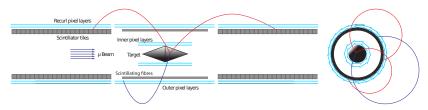

#### The Mu3e experiment, Phase-Ib configuration:

#### Key requirements:

▶ High rate: 10<sup>8</sup> muon stops on target per second

▶ Time resolution: 20 ns

▶ Vertex resolution: about 200  $\mu$ m

► Momentum resolution: about 0.5 MeV/c²

▶ Low material budget: 1‰ X₀ per pixel layer

#### Introduction

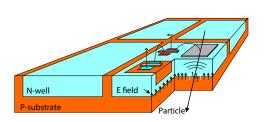

We use a High-Voltage Monolithic Pixel Sensor (HV-MAPS):

- HV CMOS technology used automotive and audio industry

- Reverse biasing up to −90 V (reliable)

- ► Thinning to  $50 \, \mu \text{m}$  possible and done

- Self-triggered, continuous readout (no shutter, darkframe etc.)

#### Introduction

#### Several generations of MuPix chips realised:

| Version                                          | Year                                    | Main features                                                                                                                                                                                                              |

|--------------------------------------------------|-----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MuPix1/2<br>MuPix3<br>MuPix4<br>MuPix6<br>MuPix7 | 2011/12<br>2013<br>2013<br>2014<br>2014 | Analog prototype chips First digital readout Working digital readout and time-stamping Readout bugs fixed, double-staged preamplifier Fast serial readout (1.25 Gbit/s), internal state machine, internal clock generation |

MuPix3–7 have an active area of  $3 \times 3 \, \text{mm}^2$ , chip size is  $3 \times 4 \, \text{mm}^2$ . MuPix7 pixel size:  $103 \times 80 \, \mu \text{m}^2$ .

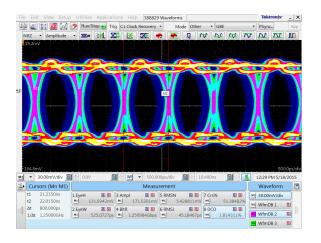

### MuPix7: Fast serial readout signal

Signal quality of fast readout signal at 1.25 Gbit/s is very good:

Clock is at 125 MHz, high speed clock internally generated. Measured on test bench using chip on standard test board.

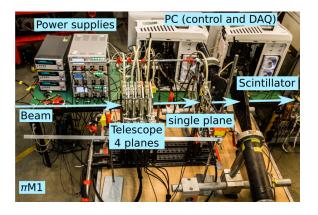

# MuPix7: Telescope

Telescope setup, e.g. at PSI  $\pi$ M1:

Telescope with 4 MuPix7 planes, 1 plane elected as DUT

#### MuPix7: Test beams

Several MuPix7 testbeam campaigns during 2015:

- Mainz MAMI, 1 GeV e<sup>-</sup> (spring)

- ▶ CERN SPS, 180 GeV  $\pi$  (July)

- PSI  $\pi$ M1, 250 MeV  $\pi^+, \mu^+, e^+$  mix (October)

- DESY, 4 GeV e<sup>+</sup> (March, October)

Over this course, the setup became more reliable. Boards were debugged with MuPix6 already, which helped a lot.

What follows is a selection of results from those campaigns.

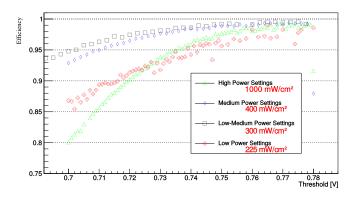

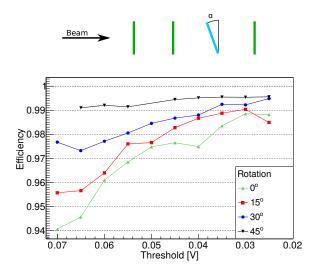

# MuPix7: Efficiency

Efficiencies of DUT in a telescope:

Technique: Extrapolate tracks to DUT. Comparing different power settings. Further optimisation planned.

Data taken at PSI

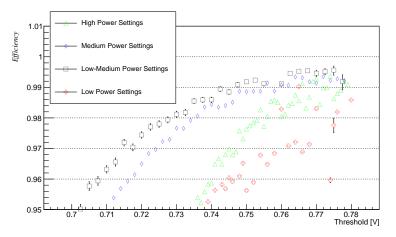

### MuPix7: Efficiency

Efficiencies of DUT in a telescope:

Same data, but zoomed in. Note: Hit rate is 300 kHz per chip. Data taken at PSI

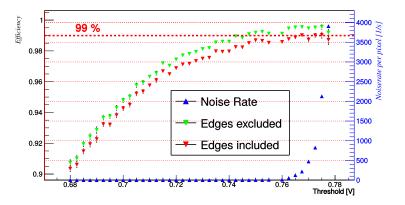

# MuPix7: Efficiency

#### Efficiencies of DUT in a telescope:

One setting (intermediate power) as example with noise rate Data taken at PSI

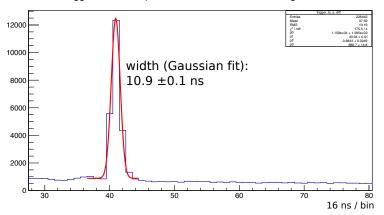

#### MuPix7: Time resolution

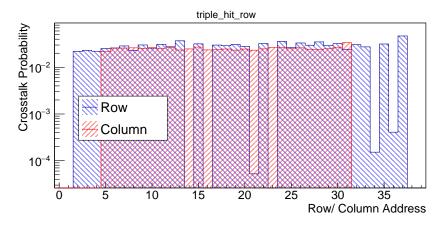

Trigger TimeStamp Difference Distribution for Single Events

Technique: Scintillator coincidence signal as reference. Plotted timestamp seen in MuPix7.

Method: Extrapolated track to DUT. Select events with 3 hits, center one matched to track. No entry: no such events found. **Do we understand the pattern?**

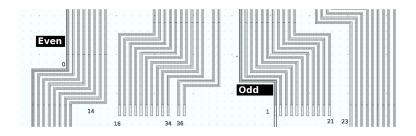

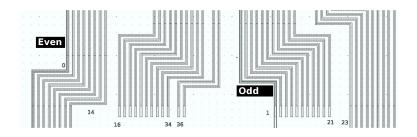

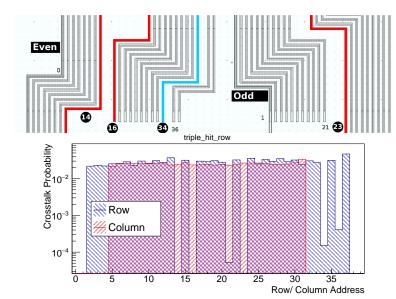

MuPix uses separate areas for analog and digital processing.

Pixel cells (sensor and preamp) are connected **point-to-point** to a corresponding digital cell (comparator, logic).

Long transmission lines can couple signals.

But still: Why the holes in the row-wise distribution?

The space distribution between lines is not uniform. Does the pattern match?

Yes. Lines of pixels 14, 16, and 23 have bigger spacing to neighboring lines, no crosstalk seen.

Column 34 has intermediate spacing, lower crosstalk.

See next slide...

# MuPix7: efficiency of tilted sensor

Efficiencies with DUT under different angles:

# MuPix7: DAQ performance

- ► CERN SPS: MuPix7 run successfully at rates of about 500 kHz (on chip)¹.

- Speed limit of MuPix7 telescope: about 1 million tracks per second. Can be increased by optimizing DMA transfer.

- ► Fast data transfer and reconstruction demonstrated (simulation and at DESY).

- Hits sorted on FPGA

- Transferred to memory using DMA

- Processed in GPU for track reconstruction.

**300 MB/s** with simulated data achieved<sup>2</sup>.

► Three MuPix7 telescopes (4 layers each) exist and proven reliable. Using own sensor and readout became a key advantage for efficient use of beamtime.

<sup>&</sup>lt;sup>1</sup>Exact rate determination difficult due to fluctuating bunch filling rate.

<sup>&</sup>lt;sup>2</sup>This is processing speed, not write to disk.

### MuPix7

#### Fact check:

|                                | Specification   | MuPix7          | Conclusion                       |

|--------------------------------|-----------------|-----------------|----------------------------------|

| Pixel size $(\mu m^2)$         | 80 × 80         | 103 × 80        | $\rightarrow$ MuPix8             |

| Sensor size (mm <sup>2</sup> ) | $20 \times 20$  | $3 \times 3$    | $\rightarrow$ MuPix8             |

| Thickness $(\mu m)$            | 50              | 50              | ok                               |

| Bandwidth per chip (Gbit/s)    | $3 \times 1.25$ | $1 \times 1.25$ | $\rightarrow$ MuPix8             |

| Hit rate (MHz/cm²)             | 2.5             | 5.5             | ok                               |

| Spatial resolution $(\mu)$     | < 100           | $103/\sqrt{12}$ | ok                               |

| Time resolution (ns)           | < 20            | 11              | ok                               |

| Efficiency (%)                 | > 99            | 99.5            | ok                               |

| Signal to noise                | > 20            | $10 \dots 15$   | $\rightarrow$ MuPix8 (substrate) |

| Power $(mW/cm^2)$              | ≤ <b>300</b>    | ≤ 300           | ok                               |

#### MuPix7

In summary, with MuPix7 we could show:

- ▶ We have a **fully functional HV-MAPS chip**,  $3 \times 3 \text{ mm}^2$

- ➤ **Specifications** met for key parameters that can be tested with MuPix7. MuPix8 is expected to cover the rest.

- ▶ Operation at high rates: 300 kHz at PSI  $\pi$ M1. We survived even higher rates of about 1 MHz at SPS.

- Crosstalk on setup under control, on chip seen. Mitigation plan exists (see MuPix8, later slides).

- ▶ We routinely operate systems of up to 8 chips in testbeams reliably.

- Data processing of one telescope (4 chips) at full rate on GPU demonstrated.

#### Goals:

- ▶ **Scaling-up** from  $3 \times 3 \text{ mm}^2$  to  $13 \times 20, \text{mm}^2$  (active area)

- All pads on one edge (required for integration studies)

- Submission deadline: June 2016 (not earlier due to foundry capabilities)

- First chip suitable for integration studies

- Options for mitigating crosstalk:

- Adjust amplifier to optimize amplitude for strong signals

- ▶ Place ground lines between signal lines

- Switch from voltage to current signalling

Chip designers are **confident** that space is sufficient to solve these issues. Next months will show.

Foundry (AMS) provides **higher-resistivity substrate** ( $20\,\Omega\text{cm} \to 80\,\Omega\text{cm}$ ). Will be explored with MuPix8 for the first time.

#### Integration studies:

- ▶ Build a **prototype of an inner layer module**: 2 × 3 chips.

- ► Studies with different **flex print options** (1 signal layer, 2 power layers):

- ▶ **Traditional:** 3 layer copper: conservative but reliable, too much material for final design  $(2\% X_0)$

- ⇒ Electrical integration studies

#### Integration studies:

- ▶ Build a **prototype of an inner layer module**: 2 × 3 chips.

- Studies with different flex print options (1 signal layer, 2 power layers):

- ▶ **Traditional:** 3 layer copper: conservative but reliable, too much material for final design  $(2\% X_0)$

- ⇒ Electrical integration studies

- ▶ **Baseline:** 1 copper layer (signal), 2 aluminium layers (power/GND), sandwiched (1.2% X<sub>0</sub> possible)

- $\Rightarrow$  Copper technology has nice spacing (10  $\mu$ m feature sizes available)

#### Integration studies:

- ▶ Build a **prototype of an inner layer module**: 2 × 3 chips.

- Studies with different flex print options (1 signal layer, 2 power layers):

- ▶ **Traditional:** 3 layer copper: conservative but reliable, too much material for final design  $(2\% X_0)$

- ⇒ Electrical integration studies

- ▶ **Baseline:** 1 copper layer (signal), 2 aluminium layers (power/GND), sandwiched (1.2‰ X<sub>0</sub> possible)

- $\Rightarrow$  Copper technology has nice spacing (10  $\mu$ m feature sizes available)

- ▶ **Optimal:** 2 layer Aluminium, if necessary with one additional layer. Uses pad-bonding  $(1\% X_0)$

- $\Rightarrow$  Technology implemented by ALICE. Riskier approach, new territory but promising.

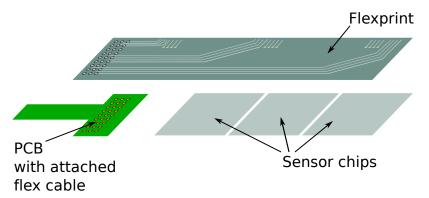

See next page for an example layout.

- Flexprints will be used to connect chips to DAQ.

- ► Two designs required (electrically split at center):

| Layers | # chips           | dimensions               | channels per chip |

|--------|-------------------|--------------------------|-------------------|

| 1,2    | $2 \times 3 = 6$  | $20\times60\text{mm}^2$  | 3                 |

| 3,4    | $2 \times 9 = 18$ | $20\times360\text{mm}^2$ | 1                 |

- Material is a challenge, of course.

- Has to provide: Power, grounding, and signals:

- ► Acceptable voltage drop: 20 mV. Remember: MuPix has no on-chip regulators (yet).

- ▶ All signals as **differential pairs**,  $Z \approx 100 \,\Omega$

- ▶ Minimal connection scheme per chip: 2 × power, HV, GND, Clk, Reset, Slow control, 3 × readout (1.25 Gbit/s)

Artistic sketch of a half-assembly fir layer 1,2:

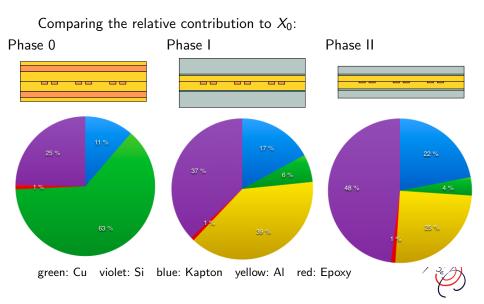

### Radiation lengths:

| Material  | $1\%$ of $X_0$ |  |

|-----------|----------------|--|

|           | $\mu$ m        |  |

| Polyimide | 286            |  |

| Cu        | 14             |  |

| Al        | 89             |  |

| Ероху     | 400            |  |

| Silicon   | 93             |  |

| Carbon    | 194            |  |

Electrical properties with radiation length in mind:

| Material    | <i>X</i> <sub>0</sub> | $\sigma$        | ρ                     | $\sigma \cdot X_0$ |

|-------------|-----------------------|-----------------|-----------------------|--------------------|

|             | cm                    | S/m             | $\Omega \cdot mm^2/m$ | S                  |

| Cu          | 1.4                   | $58 \cdot 10^6$ | $1.7 \cdot 10^{-2}$   | $8.4 \cdot 10^{5}$ |

| Al          | 8.9                   | $37 \cdot 10^6$ | $2.7\cdot 10^{-2}$    | $33 \cdot 10^5$    |

| Ratio Al/Cu | 6.4                   | 0.64            | 1.59                  | 3.9                |

For our purpose, Al is better than Cu when it comes to powering.

#### Comparing Cu options:

|                | Demonstrator      | Phase I       | PhaseII       |

|----------------|-------------------|---------------|---------------|

|                | 00 00 00          | <del></del>   |               |

| Kapton         | 45 $\mu$ m        | 45 $\mu$ m    | 45 $\mu$ m    |

| Kupfer         | $25\mu\mathrm{m}$ | 4 $\mu$ m     | $2\mu{ m m}$  |

| Aluminium      | $0\mu{ m m}$      | 50 $\mu$ m    | $25\mu{ m m}$ |

| Ероху          | $8\mu{ m m}$      | 4 $\mu$ m     | 4 $\mu$ m     |

| Silicon        | 50 $\mu$ m        | 50 $\mu$ m    | 50 $\mu$ m    |

| Kapton support | $25\mu{ m m}$     | $25\mu{ m m}$ | $25\mu{ m m}$ |

| $X_0$          | 2.17 ‰            | 1.44‰         | 1.12‰         |

#### Notes:

- ► Sketches show only the flexprint, no chip, no support

- $ightharpoonup X_0$  takes fill factor < 1 of certain layers into account

- ▶ For Phase-II, Si contributes about 50% to the material budget...

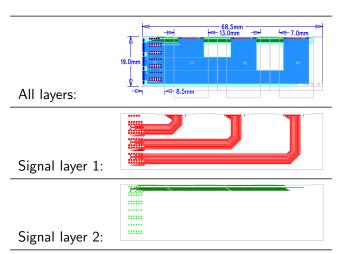

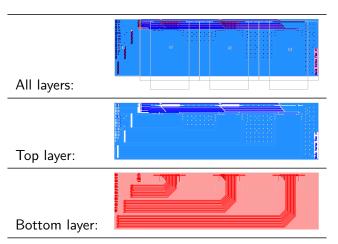

This is an example design for the two options using Cu layers (demonstrator):

M3e

Layer 1: point-to-point signals, layer 2: bus-type signals

#### LTU technology:

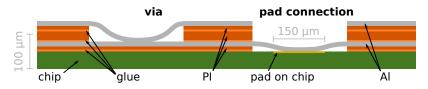

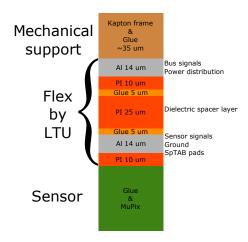

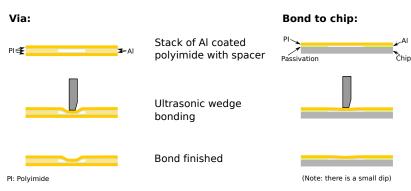

- ▶ Base material (one layer) is Al 14  $\mu$ m laminated to 19  $\mu$ m Pl

- Connections are made by tab bonding:

- No wirebonds but micro-ribbon bonds. Higher mass than wires, shorter connections. Assume no issue in B-field (needs testing).

- ▶ Mechanical sample to our drawings in hand.

This shows the stack of a typical LTU flexprint made to our spec.

This is an example design for the two options using Cu layers (demonstrator):

Layers share power/signal. Voltage drop seems at edge, optimisation will be started soon.

#### Other things not mentioned so far:

- ▶ **Capacitors** for power: will be on PCB. Power traces have a quite some area and thin spacing, will use this as extra cap.

- ► **Encapsulation** of wirebonds with traditional approaches would use too much material. Tab bonding likely solves this or we need to determine resonance frequencies and suppress them electronically.

#### Conclusions

- MuPix shows a clear path of incremental improvements over time

- MuPix7 is a fully functional HV-MAPS chip showing performance to spec

- ► MuPix8 will tackle up-scaling in size and data-rate per chip

- First integration tests will be possible with MuPix8, effort started

(Almost) no results would have been possible without the great support at all testbeam facilities (CERN, DESY<sup>3</sup>, MAMI, PSI). We gratefully acknowledge the beamtime we received.

<sup>&</sup>lt;sup>3</sup>a member of the Helmholtz Association (HGF)

# Conclusions

# **BACKUP**

### Al flexprint

#### Layer-to-layer or Layer-to-chip bonding:

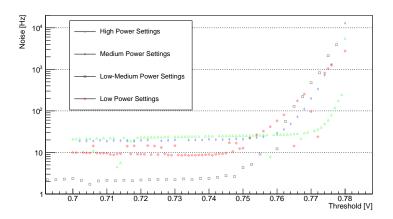

# Noise per power setting

Same measurement as shown for efficiencies, noise shown here.

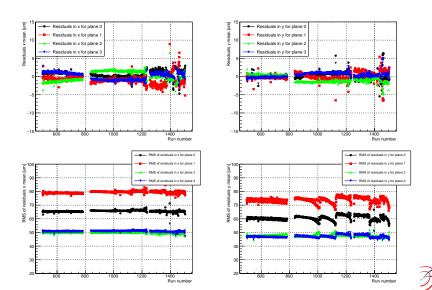

# Telescope alignment

Data taken at DESY.

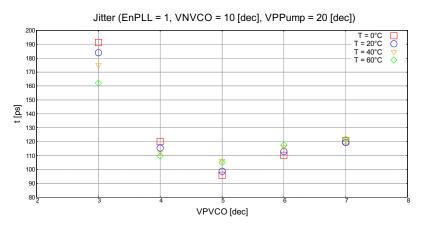

## Jitter temperature dependence

Measured in a temperature chamber. Work in progress.