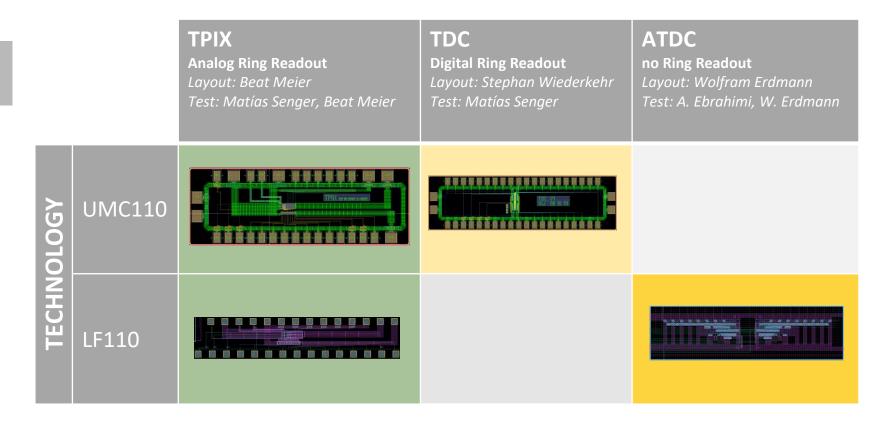

**Beat Meier :: Paul Scherrer Institut**

# TDC Development at PSI and UZH

Chip Design Meeting 20. Juni 2022

## **TDC (Time to Digital Converter)**

#### Fall 2019

## **Time Resolution Requirements**

CMS TEPX timing layer 30 ps

- Low Gain Avalanche Detectors LGAD preferred

- Project with UZH

Other Projects: 100 ps

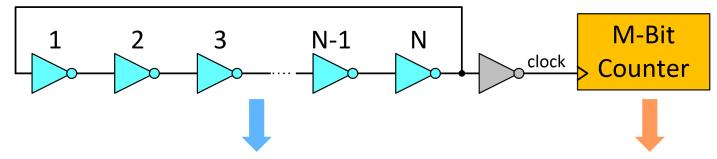

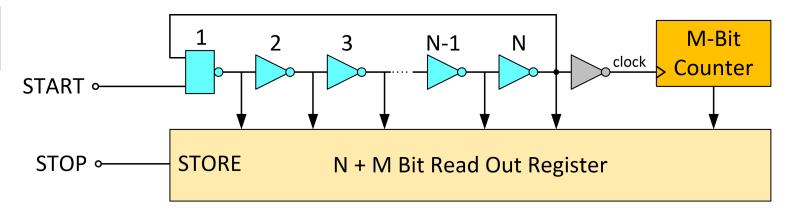

### **TDC Based on Ring Oscillator and Counter**

Ring oscillator controlled by

**START** (pixel hit)

**STOP** (reference clock)

Ring Readout (snapshot)

Fine resolution >  $t_{PD}$

Cycle Counter Readout

#### Coarse resolution >1 ns

#### Example:

- Propagation delay: 60 ps

- N = 9: T = 1 ns; f = 1 GHz

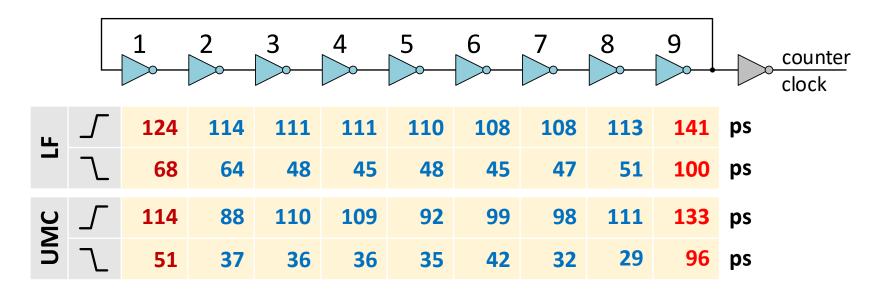

# Ring Oscillator Gate Propagation Delay $t_{PD}$

TPIX; enclosed transistors nand gates; VDD = 1.2 V

LF110 T = 1550 ps (645 MHz)  $t_{PD}$  = 86 ps

UMC110 T = 1350 ps (740 MHz)  $t_{PD}$  = 75 ps

## **TDC Fully Digital Readout**

- Easy to read out; fully digital; No ADC needed

- Huge size; only for big pixel or in periphery

- High capacitive load of ring oscillator  $\rightarrow$  high  $t_{PD} \approx 100 \ ps$

- $t_{PD}$  resolution limit (can be reduced only with another technology)

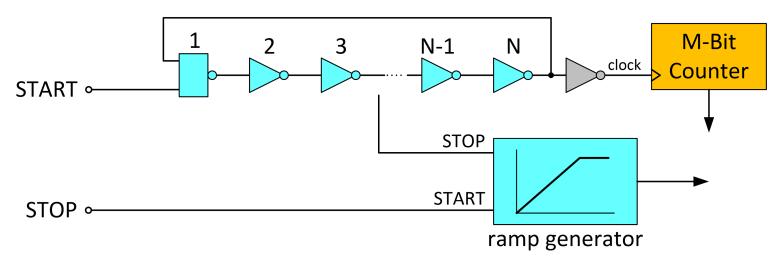

- common TDC designs

- no ring oscillator readout

- After stop, ring runs to the end

- I-C Ramp generator for sub ns resolution

- no T<sub>PD</sub> resolution limit

- time resolution limited by nonlinearity, noise of ramp generator, calibration

- higher resolution ADC for analog read out (6 bit or more)

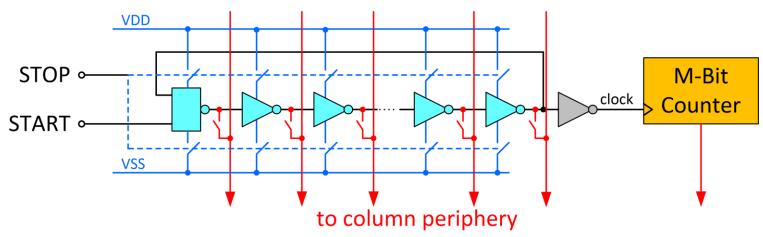

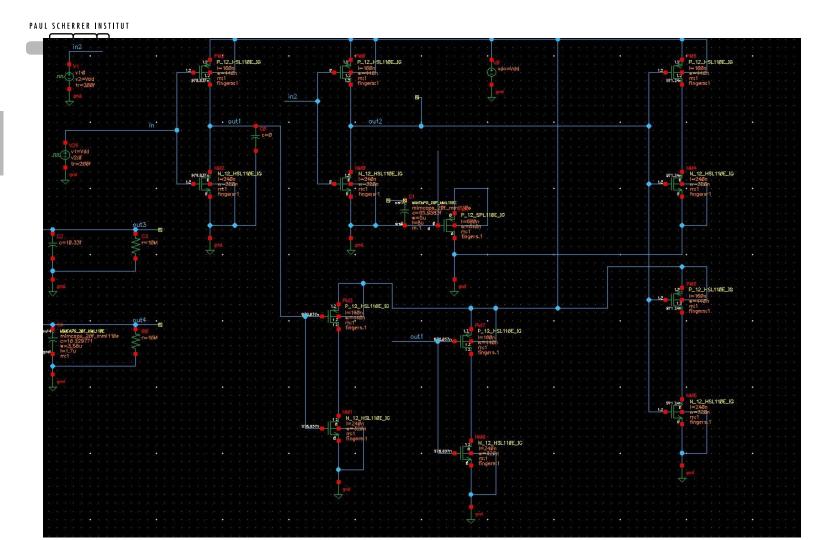

### **TPIX: Analog Ring Readout**

- Charge storage in ring oscillator

- Charge readout of a full column like a analog storage cell

- Minimal circuitry for read out

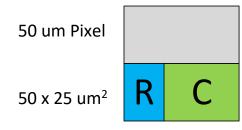

- minimal size; 50 um x 25 um

- digital readout:  $t_{PD}$  resolution limit

- analog readout: sub T<sub>PD</sub> resolution

- only 2 bit ADC needed

- High effort for analog interpolation in periphery (not yet solved)

- Non uniformity of the ring oscillator

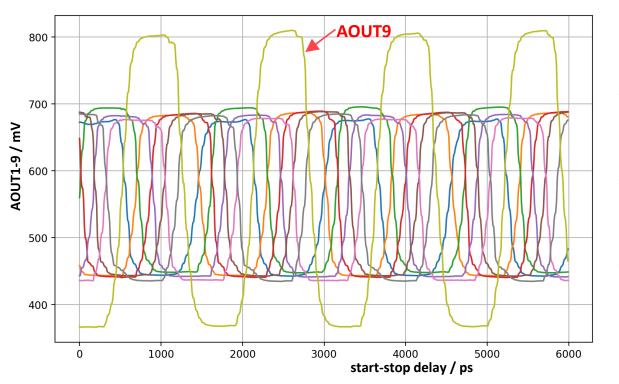

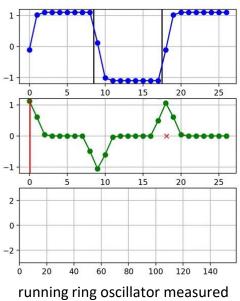

# **TPIX: Analog Read Out**

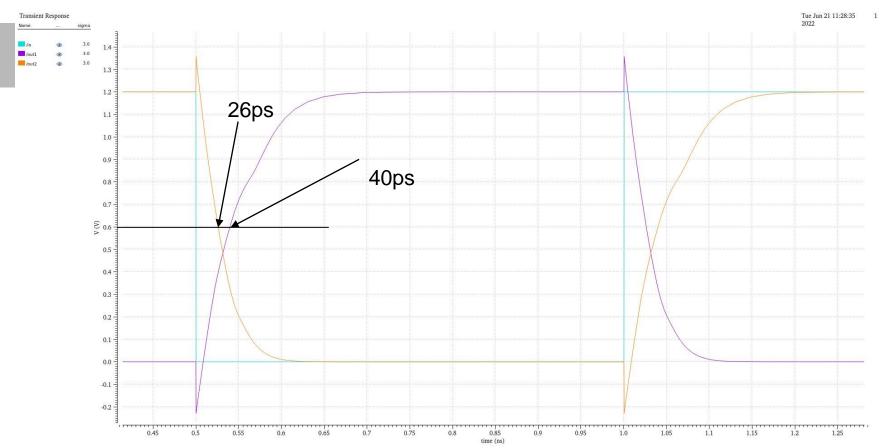

running ring oscillator measured with 1 ps time resolution

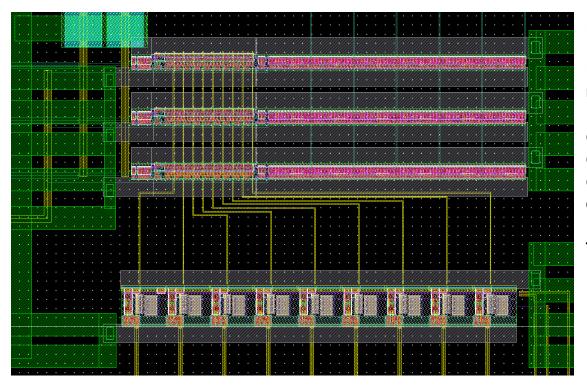

# **TPIX** required Space in Pixel (UMC)

ring stage  $4.86 \times 9.1 = 44.2 \text{ um}^2$ ring  $9 \times 44.2 \text{ um}^2 = 398 \text{ um}^2$ ring interface  $5.5 \times 9.1 = 50 \text{ um}^2$ ring area:  $450 \text{ um}^2$  36%

counter stage 21.1 x 6 = **126.6 um<sup>2</sup>** counter (6 stages) 760 um<sup>2</sup> counter interface 8.3 x 6 = 50 um<sup>2</sup> **counter area: 810 um<sup>2</sup> 64%**

Total area: 1260 um<sup>2</sup> 100%

### Integration

#### So far:

- Isolated test structures

- Ideal START/STOP signals from a test system

#### MOTIC Chip (*Stephan Burkhalter*):

- MAPS demonstrator, IFoundry

- Full pixel array

- ATDC (with analog readout) per pixel group

- Order of some 100 ps resolution ok. MAPS rather slow

#### LGAD sensor readout (Matías Senger UZH):

- Readout amplifier under test stagnates due to lack of components for the tester

- Test with LGAD + preamp/comp + TDC in Preparation

### **Next Steps**

#### Integration in a readout chip: PROC600 with TDC?

- Which readout architecture?

- TDC per Pixel? Per Column? Per Chip?

- TDC architecture is highly dependent on the application

- It is not useful to spend a lot of time in a "fantasy" architecture

#### Change to 65 nm technology

- for lower  $t_{PD}$

- to reach 30 ps resolution with digital TDC

- no analog readout (ADC) needed with TPIX

- PSI already signed NDAs for TSMC 65nm and UMC 65nm (Roberto)

- CERN NDA for TSMC 65nm where I have access

**Applications**

needed

New

Technology

~2h work!!!! Just some very rough, brainstorming-type, ideas/calculations!

#### Area calculation

- Size: 2 inverters (not min. size,p=2x n): ~1.8x1.8um2 ~ 1.62um2/inv.;

- My counter (minimal size transistors, includes storage): 4bits=28x4.6u2=32.2um2/bit (You probably do not need the storage in the counter, but you need output buffers)

- 8 gates ring osc. (3bit) + 7 bit counters=1.62x8 + 32.2um2/bit\*7=238.36; sqrt(238)=15.4

- I think every cell will need 2 inverters=1.62x16+32.2\*7=**251um2**; sqrt(251)=15.9 (10 bit equivalent)

- Estimated size for tpix: 1250um2 (~9bit equivalent)

- With linear transistors (not minimum size) you can do >2x better in terms of timing and >5x better in terms of area

- Based on "O level approximation", i.e. all timing resolution comes from tpd, the rest can be "calibrated away" (strongly doubt about that)

- Rad tol.

- Counter with minimum size transistors dies after 0.7-1Grad (but recovers after annealing)

- Digital leakage?

- More tests ongoing

- Rad. tests planned with Matterhorn 0.1