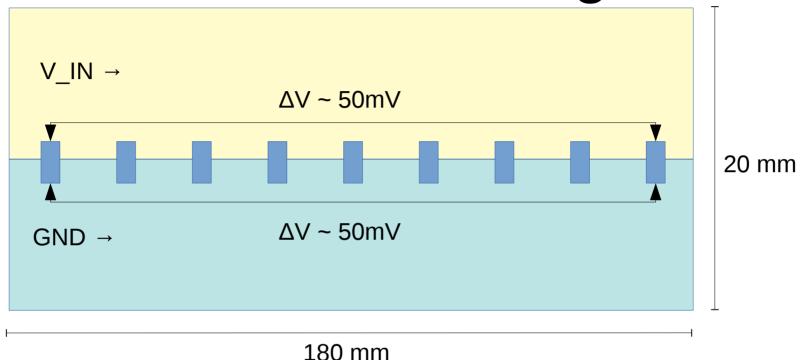

#### "Naive" Routing

- The "naive" routing scheme **minimizes** overall the power loss: **P**<sub>loss</sub>=375mW

- The summed voltage drop between sensor 1 and 9 is  $2 \times 50 = 100$  mV

$\mathbf{P}_{loss} = \mathbf{2} \cdot \mathbf{R}_{0} (\mathbf{I}_{0})^{2} \cdot \mathbf{g}$ ,  $\mathbf{R}_{0} = 2.2 \text{m}\Omega$ ,  $\mathbf{I}_{0} = 0.5 \text{A}$ ,  $\mathbf{g} = 342$  (geometrical factor)

#### 180 mm

- The "naive" routing scheme avoids voltage drops between chips;  $\Delta V = 0mV, V_{loss} = 2 \times 50mV$

- Power loss is about 450mW

$P_{loss} = 2 \cdot R_0 (I_0)^2 \cdot g$ ,  $R_0 = 2.2m\Omega$ ,  $I_0 = 0.5A$ ,  $g = n \cdot n(n+1)/2 = 405$  with n=9

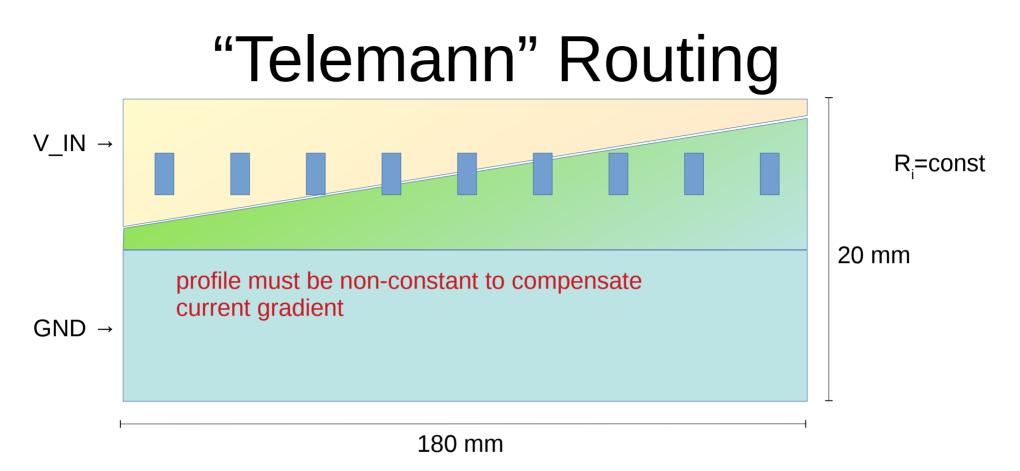

- This routing scheme **avoids** relative voltage drops between chips; but relative large voltage loss of  $V_{loss} = 2 \times 90 \text{mV}$ , all chips on slightly different potential

- Power loss is about 800 mW

$P_{loss} = 2 \cdot R_0 (I_0)^2 \cdot g$ ,  $R_0 = 2.2m\Omega$ ,  $I_0 = 0.5A$ ,  $g = n \cdot n^2 = 729$  with n = 9

A. Schöning, PI-Heidelberg

Pixel Power Meeting, Oct 2019

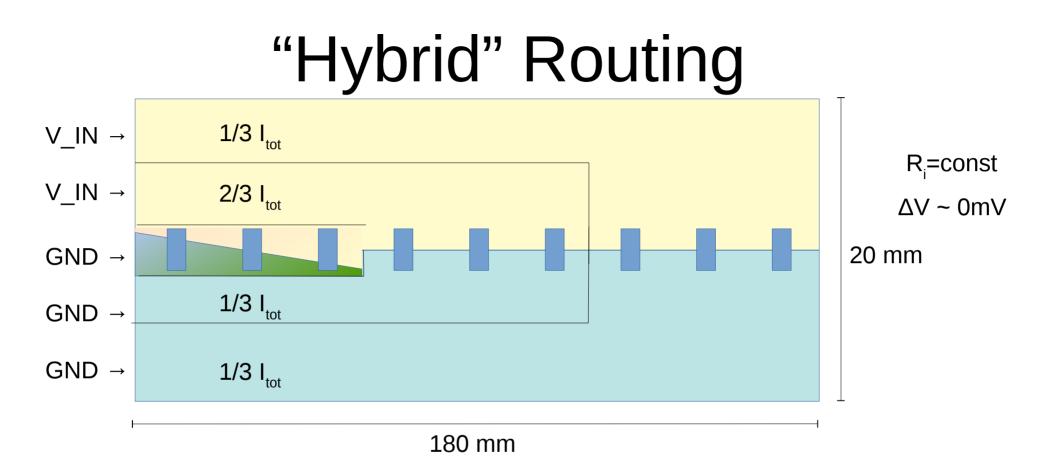

Mixture of "naive", "equal" and "teleman" methods

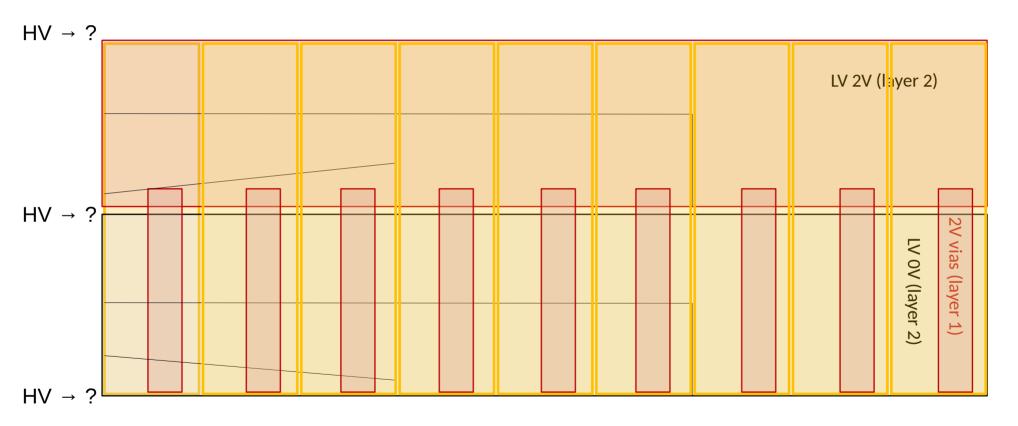

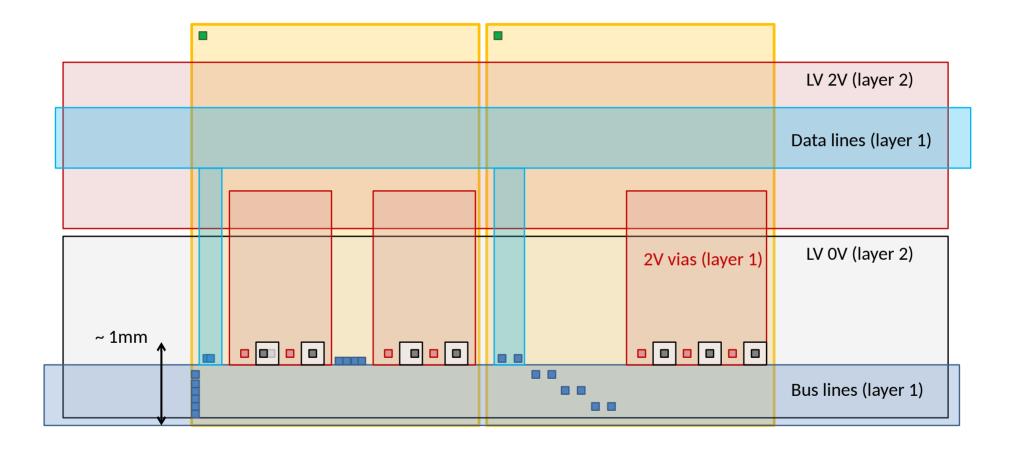

# Applied on HDI Design

possible and easy!

#### **Richard's Slide**

## Summary

- Voltage drops can be avoided by simple HDI design changes

- Exact area proportions to be simulated

### Backup

# Summary Table

Routing schemes:

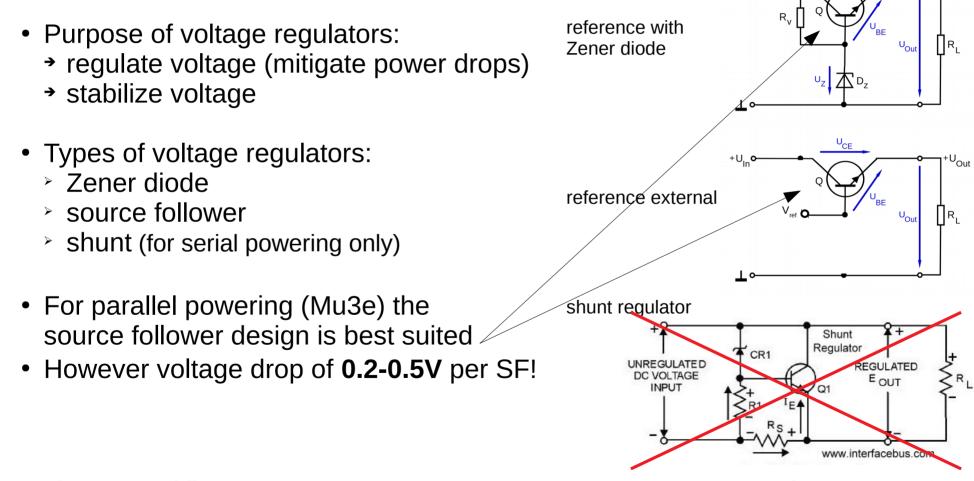

- 1) Naive Routing  $\rightarrow$  needs 2 SF (no Zener) for all currents to level out voltage drops

- 2) Equal Resistance  $\rightarrow$  needs 1 SF for all PLL and VSSA

- 3) Teleman

→ dito

4) Hybrid (Combination of 2.+3.)  $\rightarrow$  dito

| Scheme  | P <sub>loss</sub> (HDI) | #SF current                                 | P <sub>loss</sub> (SF) per<br>chip | P <sub>loff</sub> (total) | normalised<br>to 9 Watt |

|---------|-------------------------|---------------------------------------------|------------------------------------|---------------------------|-------------------------|

| Naive   | 375 mW                  | 2 x 430mA<br>@0.2-0.5V<br>2 x 70mA<br>@0.8V | 170-430 mW<br>110 mW               | 2.9-5.2 W                 | 32% - 58%               |

| Equal   | 440 mW                  | 1 x 70mA<br>@0.8V                           | 56 mW                              | 0.95 W                    | 11%                     |

| Teleman | 800 mW                  | 1 x 70mA<br>@0.8V                           | 56 mW                              | 1.30 W                    | 14%                     |

# Pixel Tracker Voltage Drops and Power Consumption

- Voltage drops on LTU-HDI due to ohmic resistance

- > spec. resistance  $\rho_{alu}$  = 2.65 10<sup>-2</sup>  $\Omega$  mm<sup>2</sup>/m (2.8?)

- → trace width 10mm, thickness  $12\mu m \rightarrow 2.2m\Omega/cm$  (oxide?)

- > Mupix power MPV=250 mW/cm<sup>2</sup> for V=2V, area=4cm<sup>2</sup>  $\rightarrow$  I<sub>Mupix</sub>=0.5A (rough estimated)

- Voltage loss in 10mm wide trace over full ladder (18cm) for 9 Mupix is  $U_{\Delta} = 200 \text{mV}$  (defines scale and worst case scenario)

- Counter measures:

- → improve HDI routing

- → use on chip voltage regulators to compensate voltage drops

- Goal: Minimize voltage drops ( $\rightarrow$  reliability) and total power consumption ( $\rightarrow$  cooling)

- Note: power consumption is the results of **loss** in traces and **voltage regulators**!

# On chip Voltage Regulators

A. Schöning, PI-Heidelberg

Pixel Power Meeting, Oct 2019

U<sub>Out</sub>

# Mupix Voltage Stabilization

Remark: I define a voltage as "stable" if it is stable against GND (noise is filtered out). If GND is noise the voltages must see the same noise!

| → level critical | ~190 mA                    |

|------------------|----------------------------|

| → level critical | ~140 mA                    |

| → stable!        | ~65 mA                     |

|                  | ~15 mA /per link           |

| → stable!        | small                      |

|                  | → level critical → stable! |

- Life becomes easier if on PLL and VSSA are stabilized using voltage regulators

- Could work if voltage levels are stabilized by clever HDI routing